Limitaciones físicas del silicio: lo que se pensaba hace 20 años.

Publicado el 1 - Mar - 2019

Hace justo ahora 20 años recopilaba de varios artículos de Internet esta información acerca de las limitaciones físicas del silicio como un handicap para el aumento de la escala de integración y la efectividad de los procesadores, así como en el proceso de su fabricación. Es interesante comprobar que difiere de la realidad lo que se pensaba que sería este mundo a principios de siglo. Os dejo con el artículo:

El futuro del silicio (1999)

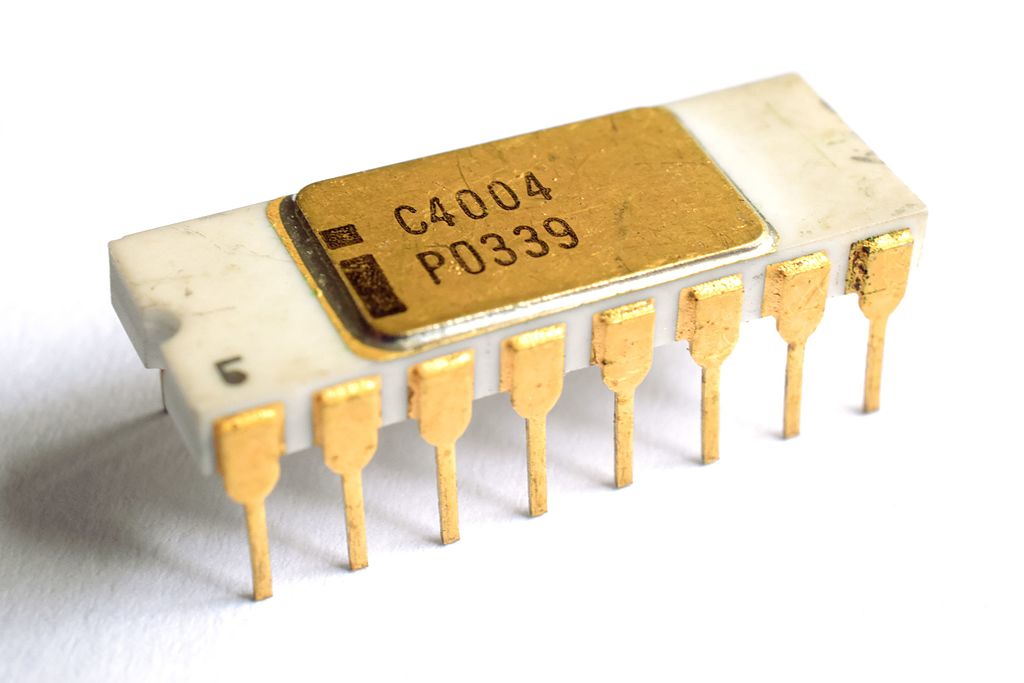

Los chips de silicio parecían tener los días contados según anunciaba uno de sus inventores, Gordon Moore, co-fundador de Intel. El primer microprocesador, tal y como lo entendemos hoy en día, fue el Intel 4004 que poseía la nada desdeñable cantidad, para la época, de 2.200 transistores y ahora IBM ha presentado un super-chip Power 4 con 170 M de transistores.

Pero la muerte del silicio llegará cuando las técnicas de miniaturización -necesarias para embutir transistores cada vez más pequeños en las cada vez más pequeñas pastillas- tropiecen con las mismas leyes de la física. Si en un principio este choque se suponía para el año 2008, esta frontera ya se traslada para el año 2020 pues la tecnología está logrando burlar a la física al menos por el momento.

Las amenazas que pesan sobre el silicio son de dos tipos: físicas y económicas. Cuanto más se avanza en un aspecto, por ejemplo en los límites físicos, más se desequilibra el otro al aumentar los costes porque la tecnología de fabricación es más cara. En el aspecto físico se trata de luchar contra propia longitud de onda de la luz, es decir, con el hecho de que los electrones se «atascan» cuando tienen que correr por «cables» cada vez más pequeños, o contra la tendencia que tienen los átomos a no permanecer estables.

La longitud de onda de la luz viene determinada por la energía del haz: cuanto mayor sea ésta más estrecho será el haz. En la construcción de chips este parámetro es crucial pues los circuitos integrados se fabrican «dibujando» con luz sobre las obleas de silicio (de forma parecida a como se revela una fotografía, salvando las distancias). Cuanto más fino sea el haz menores podrán ser los componentes.

El primer chip de Intel tenía conexiones de 10 micras (10 milésimas de milímetro), pero la última generación de microprocesadores tienen componentes de 0.18 micras y se está trabajando con la posibilidad de bajarlos a 0.10 micras. La hazaña se ha logrado utilizando un haz de luz más energético y por tanto más fino. De la luz visible se ha pasado a la ultravioleta: de las teóricas 0.13 micras que tenemos como límite podríamos pasar a las 0.07 micras si utilizamos rayos láser.

Para reducir aún más este tamaño se trabaja con Rayos X, aún más energéticos. Pero en este caso nos encontramos con el problema de la transparencia de las máscaras: hace falta encontrar un material que sea opaco a los Rayos X para fabricar las placas litográficas.

Por otro lado IBM y Lucent (filial de los Laboratorios Bell) están trabajando en un proyecto basado en un pincel de electrones para grabar en el silicio. El problema que se han encontrado es que el haz de electrones no dibuja de una vez en el circuito (como se hace hasta ahora, por capas) sino que lo hace línea a línea, de forma parecida a cómo los monitores CRT crean la imagen. No obstante ya se ha anunciado que este problema podría estar resuelto y que esta tecnología podría estar en funcionamiento sobre el año 2004.

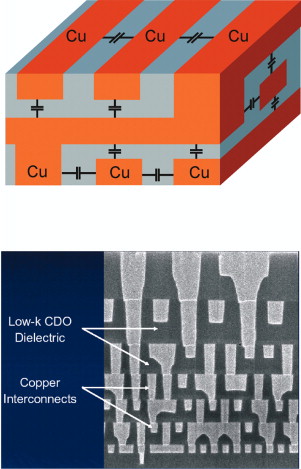

No obstante, la sucesiva miniaturización presenta efectos colaterales. Por ejemplo, a medida que los componentes del chip se hacen más pequeños las conexiones se hacen tan finas que los electrones tienen dificultades para circular rápidamente entre ellas y además se producen interferencias entre los distintos circuitos. La solución a estos problemas pasa por investigar con otros materiales diferentes a los usados actualmente. IBM ya ha dado el primer paso y ha sustituido el aluminio por el cobre en las conexiones. El cobre no se había utilizado antes, a pesar de ser más apropiado, porque interactuaba con el silicio. Pero hoy en día se ha encontrado la forma de aislar los dos materiales y el resultado ha sido que los últimos procesadores de la marca ya utilizan conexiones de cobre. Las interferencias venían dadas porque cada uno de los cables de conexión actúa como una antena que genera ruido. Estas interferencias se han evitado sellando bien cada una de las conexiones con un nuevo material del cual se conoce su nombre clave: LowK dielectric, del cual puedes aprender más en este enlace. Los primeros procesadores con esta nueva tecnología estarán en el mercado en un par de años (por el 2001).

También se busca la forma de hacer cada vez más finos los estratos de materiales con los que se construyen los chips. Por ejemplo, cuanto más delgada sea la capa de dióxido de silicio que hace de aislante en los transistores, menor voltaje se necesitará para que el transistor funcione y menor espacio ocupará. La capa que actualmente se utiliza tiene un grosor de unos 25 átomos pero se cree que se puede reducir hasta los 5 átomos aunque por debajo de este valor los transistores no funcionarían al producirse cuellos de botella.

El calentamiento de los chips supone un problema más. A media que aumenta el número de transistores en el chip y la frecuencia a la que trabajan, también crece la potencia que necesitan y el calor que deben disipar. Por esto es también importante que trabajen a menor voltaje y, por tanto, que se necesite disminuir el tamaño de la capa aislante. Las soluciones vienen por controlar el gasto energético del hardware mediante el software (básicamente el S.O.) o de diseñar el chip teniendo en cuenta el gasto energético de las operaciones que deben realizarse, por separado, para permitir que la energía se distribuya de forma no uniforme, sino el grado de actividad de las distintas zonas.

Algunos investigadores apuntan a otro problema en la carrera de la miniaturización y es el del reloj. Al hacerse el reloj cada vez más rápido se hace imposible enviar una señal de una punta a la otra del chip en un sólo ciclo. Esto hace que se tenga que pensar en distribuir el reloj por zonas cercanas, en diseñar circuitos asíncronos o en implementar trozos de chip que sólo sirvan para mandar la señal del reloj de una parte a la otra tal y como se ha hecho con los Pentium 4.

La Asociación de Industrias de Semiconductores fija cada año las fronteras de esta frenética carrera. Para el año 2014 se podrán grabar detalles de hasta 0.035 micras, los chips tendrán más de 3.000M de transistores y los procesadores tendrán unos relojes trabajando a unas frecuencias de 10GHz. Pero éste parece ser el tope definitivo. Por debajo de estos parámetros estaríamos hablando de mecánica cuántica, en la que los átomos se entretienen gastando bromas a los científicos que se ven incapaces de pronosticar su comportamiento.

Una nueva vía de investigación se está abriendo camino en esta línea: ordenadores cuánticos que aprovechan las sorprendentes propiedades del mundo subatómico y en la que la computación molecular tiene mucho que decir ( ¿ moléculas capaces de efectuar operaciones lógicas ?).

Deja una respuesta